任何高性能ADC��,尤其是射頻采樣ADC�����,輸入或前端的設計對于實現(xiàn)所需的系統(tǒng)級性能而言很關鍵�。很多情況下,射頻采樣ADC可以對幾百MHz的信號帶寬進行數(shù)字量化���。前端可以是有源(使用放大器)也可以是無源(使用變壓器或巴倫),具體取決于系統(tǒng)要求�。無論哪種情況,都必須謹慎選擇元器件���,以便實現(xiàn)在目標頻段的*優(yōu)ADC性能���。

簡介

射頻采樣ADC采用深亞微米CMOS工藝技術制造���,并且半導體器件的物理特性表明較小的晶體管尺寸支持的*大電壓也較低。因此��,在數(shù)據(jù)手冊中規(guī)定的出于可靠性原因而不應超出的優(yōu)良*大電壓���,將當前主流的射頻采樣ADC與之前的老器件相比���,可以發(fā)現(xiàn)這個電壓值是變小的。

在使用ADC對輸入信號進行數(shù)字量化的接收機應用中�����,系統(tǒng)設計人員必須密切關注優(yōu)良*大輸入電壓�����。該參數(shù)直接影響ADC的使用壽命和可靠性��。不可靠的ADC可能導致整個無線電系統(tǒng)無法使用,且更換成本也許非常巨大�。

為了抵消過壓帶來的風險,射頻采樣ADC集成了可以檢測高電平閾值的電路��,允許接收機通過自動增益控制(AGC)環(huán)路調(diào)節(jié)增益來進行補償�。但是,如果采用流水線型ADC��,則與架構(gòu)相關的固有延遲可能導致輸入暴露于高電平之下����,從而可能損害ADC輸入。本文討論了一種簡單的方法來增強AGC環(huán)路�,保護ADC。

輸入架構(gòu)

射頻采樣ADC可采用多種不同的設計����,*常見的一種是流水線架構(gòu),該架構(gòu)采用多級級聯(lián)����,將模擬信號轉(zhuǎn)換為數(shù)字信號。**級*重要���,可以是緩沖或未緩沖級��。選擇哪種設計取決于設計要求和性能目標���。例如,一個帶緩沖器的ADC通常在頻率范圍內(nèi)具有更好的SFDR性能�����,但功耗比不帶緩沖器的ADC更高���。

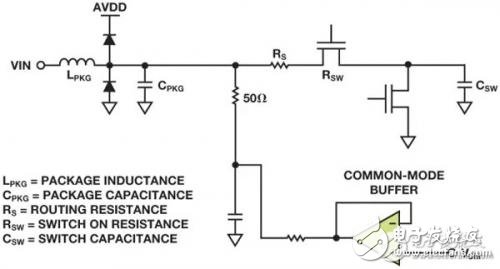

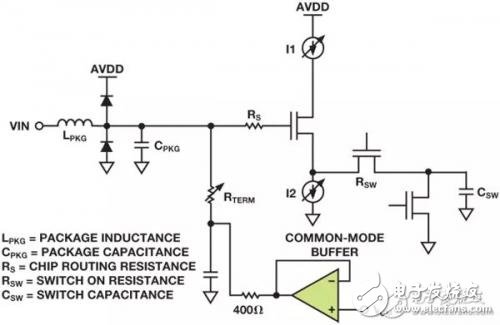

前端設計同樣會根據(jù)ADC是否有緩沖級而改變����。沒有緩沖器的ADC需要使用額外的串聯(lián)電阻來處理輸入電荷反沖����,它同樣會改善SFDR性能。圖1和圖2顯示了AD9625未緩沖和AD9680緩沖射頻采樣ADC的等效輸入電路簡化圖��。為簡明起見��,僅顯示單端輸入���。

圖1. 未緩沖射頻采樣ADC輸入的等效電路

圖2. 緩沖射頻采樣ADC輸入的等效電路

無論采用何種架構(gòu)��,ADC輸入端可持續(xù)的優(yōu)良*大電壓由MOSFET能夠處理的電壓決定���。緩沖輸入更復雜���,且比未緩沖輸入功耗更大。ADC具有多種不同類型的緩沖器�,*常見的一種是源極跟隨器。

故障機制

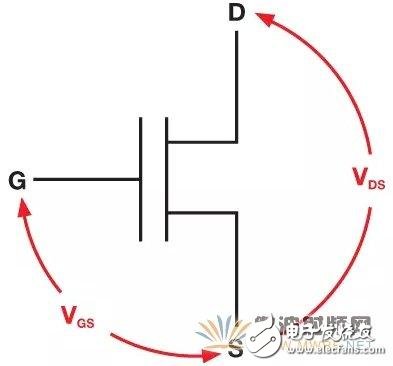

緩沖和未緩沖ADC的故障機制有所不同�,但通常是在超出允許的*大柵極-源極電壓( (VGS))或漏極-源極電壓((VDS))時發(fā)生故障。這些電壓如圖3所示�。

圖3. MOS晶體管的關鍵電壓

例如,假設VDS超過允許的*大電壓����,則發(fā)生VDS擊穿故障,這通常在MOSFET處于關斷狀態(tài)且在漏極施加了相對于源極的過量電壓時發(fā)生���。如果VGS超過允許的*大電壓�,則它會導致VGS擊穿(亦稱為氧化層擊穿)���。這通常在MOSFET處于導通狀態(tài)且在柵極施加了相對于源極的過量電壓時發(fā)生����。

未緩沖ADC的故障機制

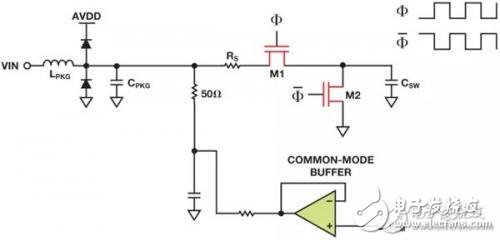

圖4顯示的是一個未緩沖ADC輸入。采樣過程由反相時鐘信號Φ和Φ控制����,它們是MOSFET M1的采樣/保持信號以及MOSFET M2的復位信號��。M1導通時�,M2關斷,且電容CSW跟蹤信號(采樣或跟蹤模式)�。當M1關斷時,MDAC中的比較器作出判斷后M2導通�,電容CSW復位。這樣可在采樣階段使采樣電容為下一次采樣做好準備�����。該電路通常工作狀態(tài)優(yōu)良����。

但是,高壓輸入使M2暴露在超出其漏源電壓的應力之下���。當對輸入高壓進行采樣(M1導通��、M2關斷)時���,M2會暴露于較大的VDS之下����,其在不足采樣時鐘半周期的時間內(nèi)處于關斷狀態(tài)����,但哪怕只是瞬時的暴露也會降低電路的可靠性,導致ADC隨時間失效�。在復位模式下(M1關斷、M2導通)���,因M1的漏極上有輸入信號�����,從而也會暴露于大的VDS電壓����。

圖4. 未緩沖ADC輸入的故障模式

緩沖ADC的故障機制

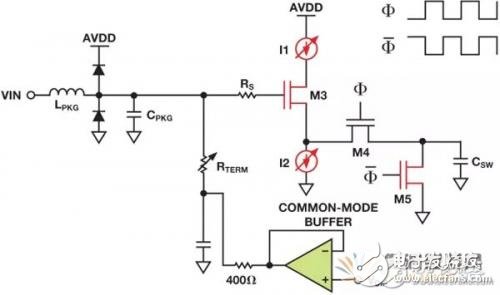

圖5顯示的是一個緩沖ADC輸入��。采樣和復位信號適用相同的時鐘方案���。無論相位如何�,當緩沖器M3柵極暴露于高壓輸入時,產(chǎn)生電流I1以及I2�����。電流源I1采用PMOS晶體管實現(xiàn)��,而I2采用NMOS晶體管實現(xiàn)��。M3柵極上的高電壓導致I1和I2 MOSFET產(chǎn)生過大的VDS��。此外��,M3柵極上的高電壓還可導致氧化層擊穿����。

圖5. 緩沖ADC輸入的故障模式

緩沖和未緩沖ADC的擊穿機制有所不同����,因此優(yōu)良*大輸入電壓同樣有所不同,如表1所以�。